# **International Journal of Computing and Digital Systems**

http://dx.doi.org/10.12785/ijcds/020308

# Chaos: A Nonlinear Phenomenon in AC-DC Power-Factor-Corrected Boost Convertor

# Arnab Ghosh<sup>1</sup>, Pradip Kumar Saha<sup>2</sup> and Goutam Kumar Panda<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, National Institute of Technology, Durgapur, India <sup>2</sup>Department of Electrical Engineering, Jalpaiguri Govt. Engineering College, Jalpaiguri, India

E-mail addresses: arnab.4u2010@gmail.com, p\_ksaha@rediffmail.com, g\_panda@rediffmail.com

Received 31 Jul. 2012, Revised 20 Dec. 2012, Accepted 30 Jan. 2013, Published 1 Sep. 2013

**Abstract:** Nonlinear Dynamics is a very popular topic for researchers. The prior researchers already studied the nonlinear dynamics of current controlled DC-DC boost converter. The power factor corrected boost regulator is a circuit which is designed especially as input power factor can maintain unity. Firstly, we derive the state equations of this switching circuit. The circuit is numerically simulated by MATLAB Simulink module. Here load resistance is taken the major parameter for observing the system dynamics. The fundamental, subharmonic, and chaotic orbits are reported after getting simulation results. The paper also proposes a control system that automatically stabilizes one-dimensional time-delayed chaotic system. The delayed-feedback control (DFC) is proposed to stabilize the unstable periodic orbit (UPO) as it is not accepted for designing the practical power supply.

Keywords: PFC Boost Regulator; State Equations; Phase-Plane Trajectories; Chaos; Chaos Control.

## I. INTRODUCTION

The studies of complex behaviour in switching power converters have gained increasingly more attention from both the academic community and the industry. This switched ac-dc power factor correction boost converter [1] provides dc voltage at the output end with having high input power factor. A low power factor decreases the power level in the utility grid, with a high harmonic distortion to the line current that causes EMI problems. It is usually assumed ripple free output by considering a huge output capacitor to load side, which is not acceptable in design due its bulky size and cost. Thus this system is designed to ensure a minimum distortion and circuits used to achieve unity power.

Various kinds of nonlinear phenomena, such as bifurcation and chaos have been revealed [2][3]. Chaos could be described as noise like, bounded oscillations with an infinite period found in nonlinear, deterministic systems [4]. These complex behaviours implying instability can be observed by changing circuit parameters. The occurrence of bifurcation and chaos in

power electronics was first reported in the literature in the late 80's [5][6].

The route to chaos in a current controlled boost converter was first discussed by Deane [7]. Chan and Tse [8], S. Banarjee and K. Chakrabarty [9] studied various types of routes to chaos and their dependence upon the choice of bifurcation parameters. The nonlinear dynamics of PFC boost converter has been reported [10].

The prior researchers described the control of Chaos depending on small, time-dependent parameter or input perturbations [11] [12]. Some other different strategies to control chaotic dynamics have been proposed in recent surveys [13], [14], [15]. Pyragas proposed *Time-Delayed Auto Synchronization (TDAS)* [16]. Socolar reported *Extended Time-Delayed Auto Synchronization (ETDAS)*[17].

In this paper, the power-factor-correction boost convertor is considered continuous conduction mode to analyse its nonlinear behaviours. Firstly, the designing and simulation aspects of current-mode controlled *pfc* boost

This work is supported by the research grant of Govt. of India.

convertor are operating in chaotic regime. Secondly, is used to chaos controller to control the chaotic region.

#### II. CIRCUIT DESIGNING CONCEPT

In power-factor-correction converter the input line voltage and current are in almost same phase (*i.e.* unity *pf*) with considering almost ripple free output voltage. Here active circuit of utility interference is designed for shaping the input line current by using power electronic converter.

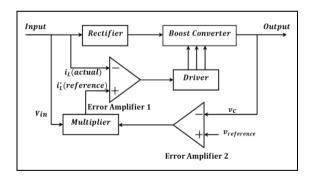

Based on these considerations,  $v_C > V_{in}$ , where  $V_{in}$  is the peak of the ac input voltage  $v_{in}$ . Therefore, the obvious choice for the current shaping circuit is a step-up ac-dc converter. The output capacitor,  $C_d$  is designed to minimize the output voltage ripple in  $v_C$ . Because the input current to the step-up converter is to be shaped, the step-up converter is operated in a current-regulated mode. The feedback control is shown in a block diagram form in Fig. 1, where  $i_L^*(reference)$  is the reference or the desired value of the current  $i_I(actual)$ . The amplitude of  $i_L^*(reference)$  should be maintained by multiplier block. The error voltage  $v_e$  from the Error Amplifier 2 then is fed to the multiplier and multiplied with input voltage to get the  $i_L^*(reference)$ . The error  $i_e$  that is the output of Error Amplifier1, as the difference of  $i_L(actual)$  and  $i_L^*$  (reference) provides the correct timing logic for the switching driver circuit to turn on and off the Boost converter (Only Constant-Frequency considered).

Fig. 1. PFC control strategy block diagram [1]

## III. STATE EQUATIONS

The two pairs of state equations [1] of the circuit depending on state of the power switch. When switch is = closed, the inductor current rises with ignoring any clock \_ pulse arriving during that period. The switch opens when current reaches the reference current. When switch is open, the current falls until the arrival of next clock pulse.

1). The State Equations during "ON" period

$$\begin{cases} \frac{di_L}{dt} = \frac{V_{in}}{L} \\ \frac{dv_c}{dt} = -\frac{v_c}{RC} \end{cases}$$

(1)

2). The State Equations during "OFF" period

$$\begin{cases} \frac{di_L}{dt} = \frac{V_{in}}{L} - \frac{v_c}{L} \\ \frac{dv_c}{dt} = \frac{Ri_L - v_c}{RC} \end{cases}$$

(2)

Where,

$V_{in}$  = Input Voltage, L = Inductor, C = Capacitor,  $i_L$  = Inductor Current,  $v_C$  = Capacitor Voltage.

#### IV. PROPOSED MODEL

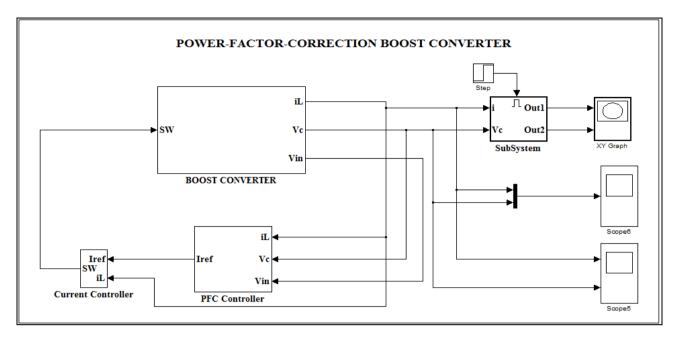

Many prior researchers investigated the current-mode control dc-dc boost converter with considering linearized models. Those circumstances some assumptions implied to direct the system toward linear models[1]. They assumed that the output ripple is neglected by using a huge output capacitor, which is not acceptable in design due to its bulky cost and size. Also the input time-varying voltage was replaced with its root mean square (rms). With taking all these assumptions, the linear system was derived ignoring the effect of nonlinearity, introduce a small-signal equivalent circuit, and discussed the stability problem depending on these linear treatments. The main feature of this *pfc* circuit is the use of a multiplier that introduces its nonlinearity. The circuit modelling and simulation are done by MATLAB (Fig. 2).

# V. PHASE PLANE TRAJECTORIES

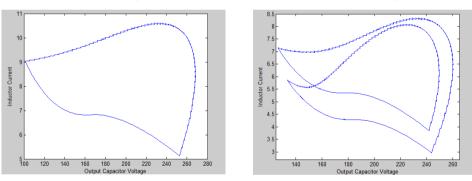

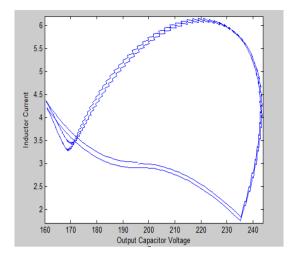

The Simulation model is totally designed by Simulink blocks. The phase-plane trajectory is constructed between the output capacitor voltage  $v_C$  and the inductor current  $i_L$ . The phase-plane trajectories are shown below.

TABLE I: Values for System Parameters

| Symbol   | Quantity                 | Designed Values for Parameters       |

|----------|--------------------------|--------------------------------------|

| $v_{in}$ | Input Voltage            | $220\sqrt{2}\sin \omega t Volt$      |

| L        | Inductor                 | 40mH                                 |

| C        | Capacitor                | $100\mu F$                           |

| $f_s$    | Switching Frequency (SW) | 20kHz                                |

| R        | Load Resistance          | $35\Omega$ / $45\Omega$ / $67\Omega$ |

Fig. 2. Boost PFC ac-dc regulator under fixed frequency current mode control. [1]

# **Diagrams of Phase-Plane Trajectories**

# B. Case II(Period II Operation)

Fig. 3. Phase Plane Trajectory (Case I) [1] Fig. 4. Phase Plane Trajectory (Case II) [1] Capacitor Voltage vs. Inductor Current (Period I operation) Capacitor Voltage vs. Inductor Current (Period II operation)

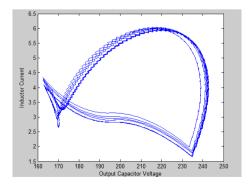

## C. Case III(Chaotic Mode Operation)

Fig. 5. Phase Plane Trajectory (Case III) [1] Capacitor Voltage vs. Inductor Current (Chaotic Mode Operation)

## A. Fundamental and Subharmonic Orbits

The *fundamental periodic* operation which is the most acceptable operation employed in practical power supplies. In this operation, waveforms repeat at the same rate *i.e.* after one cycle with the externally driving clock pulse. It is also known as "*Period–I operation*". The corresponding phase portrait is shown in Fig. 3 [1] which demonstrates the stable and periodic nature of the system. Similarly *period-two subharmonic* operation is shown in Fig. 4 [1] *i.e.* state variables repeat after "2" cycles, so it is a "*Period II operation*". It is worth noting that

subharmonic operations have never been considered in the practical design of power supplies despite the fact that they are stable.

#### B. Chaotic Orbits

The phase portrait of chaotically operating circuit is shown in Fig. 5 [1]. The state variables *i.e.* inductor current and output capacitor voltage repeats after "n" times, so it is a "*Chaotic mode operation*". Conventional power supply designers have always banned this type of operation in their final products.

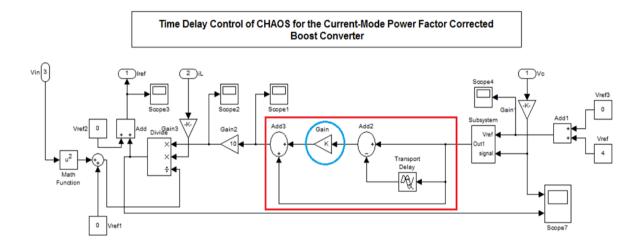

Fig. 6(a). MATLAB Model of Time Delay Feedback System (TDS) Control of Chaos of PFC Controller Block. [1]

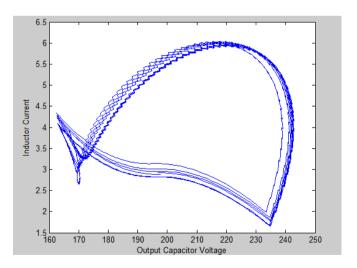

## **BEFORE CONTROLLING CHAOS**

Fig. 6(b). Phase Portrait of Capacitor Voltage vs. Inductor Current before Controlling Chaos.

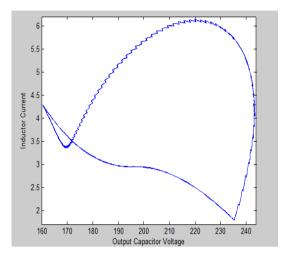

#### AFTER CONTROLLING CHAOS

Fig. 7. Phase Portrait of Capacitor Voltage vs. Inductor Current after Controlling Chaos (K= 4).

Fig. 8. Phase Portrait of Capacitor Voltage vs. Inductor Current after Controlling Chaos (K= 1).

## VI. CONTROL OF CHAOS

Time Delay Feedback System (TDS) is picked up for controlling the Chaos. Our strategy to stabilize the UPO by modifying the reference current with a term proportional to the difference between a linear combination of the present and past states of the system. The Chaotic mode phase portrait is shown in Fig. 5; the Time Delay Feedback System is used for controlling the chaos which is marked as a square in Fig. 6 (a). The circular shape is denoted the gain K of the chaos controller (marked in Fig. 6 (a)). The gain K is varied and observes the phase-plane trajectories in Fig. 7 & 8 after controlling the chaos. "Period I" and "Period II" operation observe at K = 4 & 1 respectively.

#### VII. CONCLUSIONS

In this paper we describe the nonlinear phenomena like chaos of ac-dc current controlled power-factorcorrection boost convertor. Here we have been investigated with considering the nonlinear model. The phase-plane-trajectories are observed by varying value of load resistance R where output capacitor voltage (VC) and inductor current ( $i_L$ ) are considered as state variables. The phase-portrait of output capacitor voltage (  $\mathcal{VC}$ ) and inductor current ( $i_L$ ) is going to "period I" to "period II" to "chaotic-mode" by increasing or decreasing the value of load resistance R. Chaotic phenomena are understood by multiple loops on phaseplane diagram. The most important point is to control the chaos and it is done by time delay feedback system (TDS). We can control entire system in our desired region i.e. "period I", "period II" according to our demand. The

simulation results and figures are also agreed with our statements.

#### ACKNOWLEDGMENT

I am very grateful to Professor Soumitra Banerjee at Indian Institute of Science and Research, Kolkata and Professor Mohamed Orabi, Director of the Aswan Power Electronics Application Research Center, Faculty of Engineering, South Valley University, Aswan, Egypt for their suggestions.

## REFERENCES

- [1] Arnab Ghosh, Dr. Pradip Kumar Saha and Dr. Gautam Kumar Panda, "Chaos and Control of Chaos in Current Controlled Power Factor Corrected AC-DC Boost Regulator" in Int. J. of Modern Engineering Research, Volume 2, Issue 4, pp. 2529-2533, July–August 2012.

- [2] J. R. wood, "A Chaos: a real phenomenon in power electronics," IEEE Transactions on Power Electronic, 1989.

- [3] D. C. Hamill, "A field rich in nonlinear dynamics: in nonlinear dynamics of electronic systems," IEEE Transactions on Power Electronics, 1995.

- [4] E. Colon, F. Rodriguez, U. Contreras, "Development of tools for the study of chaotic behavior in power electronics," in Proc. 2000 IEEE Computers in Power Electronics Conf., pp. 177-182.

- [5] D. C. Hamill, D. J. Jefferies "Subharmonics and chaos in a controlled switched-mode power converter," IEEE Trans. Circuits Syst. I, vol. 35, pp. 1059-1061, Aug. 1988.

- [6] D. C. Hamill, J. H. B. Deane, "Instability, subharomnics and chaos in power electronics systems," IEEE Trans Power Electron, vol. 5, pp.260-268, July. 1990.

- [7] J. H. B. Deane, "Chaos in a current-mode controlled boost DC-DC converter," IEEE Trans Circuits Syst. I, vol. 39, pp.680-683, Aug. 1992.

- [8] W. C. Y. Chan, C. K. Tse, "Study of bifurcation in current- programmed boost dc-dc converters: From quasi-periodicity to period doubling," IEEE Trans Circuits syst. I, vol.44, pp. 1129-1142, Dec. 1997.

- [9] S. Banarjee, K. Chakrabarty, "Nonlinear modeling and bifurcations in the boost converter," IEEE Trans. Power Electron., vol. 13, pp. 252-260, 1998.

- [10] A. Aroudi, M. Orabi, "Stabilizing Technique for AC-DC Boost PFC Converter Based on Time Delay Feedback," IEEE Trans. on Circuits and Systems-II, vol. 57, pp.56-60, 2010.

- [11] E. Ott, C. Grebogi, and J. Yorke, *Controlling chaos*, Phys. Rev. Lett., vol. 64, pp. 1196-1199, 1990.

- [12] T. Shinbrot, C. Grebogi, E. Ott, and J. Yorke, *Using small perturbations to control chaos*, Nature, vol. 363, pp. 411-417, 1993.

- [13] G. Chen and X. Dong, From Chaos to Order: Methodologies, Perspectives and Applications. Singapore: World Scientific, 1998.

- [14] F. Chernouskoand A. Fradkov (eds.), Proc. 1st International Conference on Control of Oscillations and Chaos, IEEE, 1997. (St. Petersburg, Russia), August 1997.

- [15] T. Kapitaniak, Controlling Chaos. San Diego, CA: Academic Press, 1996.

- [16] K. Pyragas, Continuous control of chaos by selfcontrolling feedback, Phys. Lett., vol. A170, pp. 421-428, 1992.

- [17] J. Socolar, D. Sukow, and D. Gauthier, Stabilizing unstable periodic orbits in fast dynamical systems, Phys. Rev. E, vol. 50, pp. 3245-3248, 1994.

Arnab Ghosh received B.Tech (Electrical) from JIS College of Engineering, Kalyani, M.Tech (Electrical) Specialization: Power Electronics & Drives from Jalpaiguri Govt. Engineering College, Jalpaiguri. He is currently Research Electrical Scholar, Engineering Department, National Institute of Technology, Durgapur, West Bengal.

His area of interest is to study nonlinear dynamics of power electronic circuits.

Pradip Kumar Saha received BE (Electrical) from B.E.College, Shibpore. M.Tech((Electrical) Specialization: Machine Drives & Power Electronics from IIT-Kharagpur. Ph.D from University of North Bengal. FIE, MISTE, Certified Energy Auditor. He is currently a Professor and Head, Department of Electrical

Engineering, Jalpaiguri Government Engineering College, Jalpaiguri, WB-735102. His research interests include chaotic dynamics in drives and power electronics.

Goutam Kumar Panda received BE (Electrical) from J.G.E. College, Jalpaiguri, M.E.E (Electrical) Specialization: Electrical Machines & Drives from Jadavpur University. Ph.D from University of North Bengal. FIE, MISTE, Certified Energy Auditor. He is currently Professor, Department of Electrical Engineering, Jalpaiguri Government

Engineering College, Jalpaiguri, WB.