http://dx.doi.org/10.12785/ijcds/050603

# Static Noise Margin Enhanced in FinFET Based 10T SRAM Cell at 45 nm using EDA Tool

Varun Sable<sup>1</sup>, Shyam Akashe<sup>2</sup>

<sup>1</sup>Assistant. Professor in EC Department of MIST, Indore(M.P.),India <sup>2</sup>Professor in EC Department of ITM University, Gwalior(M.P.), India

Received 21 Mar. 2016, Revised 7 May 2016, Accepted 5Sep. 2016, Published 1Nov. 2016

Abstract: We introduce the parameter that especially affects the stability i.e. Noise. Actually for every Static Random Access Memory (SRAM) cell there is a fix Static Noise Margin (SNM) is present which shows margin of the stability in operations of the SRAM cells. We can analyze the SRAM cells stability and this is done by SNM investigation in read, write and hold mode. In VLSI design, there are many devices facing different-different problems in that concern SRAM cells are defeats the instability of write ability as the technology scaling down destructively. SRAM cells has a dynamic role in a microchip worlds but the scaling down of technology increases the leakage problems more than 40 to 45% than the average power is waste, so due to the leakage and short channel effects. Mostly Complementary Metal Oxide Semiconductors (CMOS) based 7T SRAM Cell has less noise affected due to its one extra transistors controls the output value as compare to 6T SRAM Cells and 10T SRAM Cell. In this paper we work on the FinFET based 10T SRAM Cell that has more controllability over 7T SRAM Cell. So, if we reduce the phenomenon condition of the 10T SRAM Cell that have more FinFET required to build the cell than we can easily reduce the 6T as well as 7T SRAM Cell It reduces the possibility to loss of signals and data. By comparing 7T SRAM Cell and 10T SRAM Cell provides better SNM due to its symmetric & more access controls Cells working. Here, we compare the 7T and 10T SRAM Cell because 7T SRAM Cell has very good SNM than all SRAM cells hierarchy.

Keywords:SNM; 7T SRAM Cell; 10T SRAM Cell; Controllability; CMOS; FinFET.

# 1. INTRODUCTION

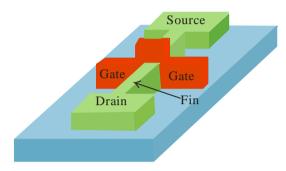

In any Integrated Chips (IC's), memory Cells stability and speed value depends on the average value of the Noise voltage is either Integrated or Spot Noise and resultant value depends on Static Noise Margin [1]. Technologies are reaches towards nanometer range and in these complexities increases due to short channel effect; but the design engineers can only change the cell size of transistors but can't able to remove the drawbacks. The cell ratio (CR) and Pull up Ratio (PR) can be controlled by engineers and by varying these parameters [2], we can control the whole circuitry factors and working. In industries, the circuits and electronics machinery are working on 45nm or less than 45nm technology. Now, the industries are focusing on VLSI circuits that are capable to works on low supply voltages. It affects the SRAM cell performance, variation in data and also reduces the SNM range. The new up-coming performance metric per unit power (Koomey's law), one of the major design optimization alternative is FinFETs, as compared to the planar technology, is much better performance at the same power budget. The FinFETs introduces much higher complexities for resistance and parasitic capacitance [3]. FinFET have many boons over bulk the MOSFETs this are: leakage reduction, subthreshold level better and voltage gain provide good result. This makes them eye-catching for digital circuitry and low frequency applications, in which the power factor is more important from all parameters. But in highfrequency applications, CMOS based MOSFETs are taken crown of advantage over FinFETs because of their fix threshold and higher transconductance. The FinFET diagram is shown in figure 1 Cross sectional view of FinFET. FinFET has two broad divisions in SOI and bulk FinFET. Short channel effect and high doping cons. Found in bulk FinFET compare to SOI FinFET [4]-[5]. So, FinFET on silicon on insulator is preferred over bulk FinFET [6].

Double gate MOSFET and MuGFET are floating body devices into which charge trapping occurs in body this causes leakage due to radiation. Charge trapping occurs due to 'back channel interface' and 'total dose latch effect' [7]. Trapping in buried oxide potential of body modulates, when depletion between source and body is lower than electrons injected into the body and drain region collect it [8].If electric field is high to cause impact ionization in drain occur and lead to current runaway causing snapback [9].

Figure 1. Cross sectional view of FinFET device

For low power application threshold get lowered which also contributes leakage currents. There are many common ways of designing any circuits. One such method is to reduce the power supply around or below threshold voltage [10]-[11]. But lowering the nominal voltage has to sacrifice its functioning to some extent and consequences of lowering the supply voltage are embarrassment in stability of cell, noise margin, on current to off current ratio and strong sensitivity to PVT (process voltage temperature) variations [12]. There are various leakage reduction approaches for both during standby mode and run time that is when the circuit is in operation. The new generation devices we need speed and better storage fast accessing. So, SRAM Cell is fast accessing and storage device [13]. In mobile and RADAR applications, SRAM Cells used with high density on chips, concerns towards excessive power consumption. Scaling down technology affects rise in dissipation of power and other glitches, like noise margin responsibility to get lower for cell firmness arises in bulk 4T and 6T SRAM Cells [14].

For resolving these issues, we analyses the number of FinFET based SRAM Cells topologies that able to operate in a sub threshold voltage successfully. In this paper, we have evaluated the SNM for FinFET based 10T SRAM Cell. Also, we evaluate the SNM curve for write mode because 10T SRAM Cell provide better write ability compare to 7T or 6T SRAM Cells. In many SRAM Cells there is write ability issues affects due to transistors works in sub-threshold region. So, to avoid these issues we switched from 6T, 7T to 10T SRAM Cell.In this paper, we did sectioning of whole paper section 2 gives the brief about working of conventional 10T SRAM Cell then section3 detailed about why FinFET based 10T SRAM Cell and its features. Section 3 contains the transistor width modulation effect and which parameters get affect over SNM and at last section gives the description of SNM.

# 2. CONVENTIONAL 10T SRAM CELL

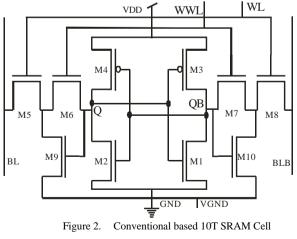

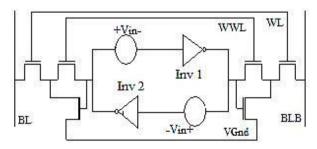

10T SRAM Cell is connection of two CMOS inverters cross coupled to each other with two transistors both side to access the data of the bit lines BL and BLB that's why it is known as access transistors which shown in figure 2 Conventional based 10T SRAM Cell as M5, M6, M7 and M8 transistors. Out of M6 & M7 controlled by WWL and M5 & M8 is controlled by WL line. Here, two write lines help to increase the write accessibility and also help to reduce the condition of leakage at the time of rise time, fall time and in hold mode. M9 & M10 transistors provides feedback path for M6 & M7 to avoid the loss of data and also retain the voltage in its current state. For M9 & M10 transistors provided separate ground VGND which can vary from 0 to 0.25 V so that we can reduce the sweeping level [15].In read mode, VGND is moving 1 to 0 V and WL are getting high while WWL remain disabled. The data nodes decoupled due to WWL disabled transistors from bit and bit-bar lines. Due to this separation, the SNM of read and hold mode is same in 10T SRAM Cell [16]. The read mode stability is curiously enhanced in 10T SRAM Cell; because hold mode is much larger than 6T SRAM Cell. Depending on the cell data values Q & OB, one of the bit-lines starts discharging after WL is enabled.

During write mode, WL and WWL are goes 0 to 1 for transferring the write value to cell node from bit-lines. During hold mode WL and WWL values are goes 1 to 0 and access transistors get disabled and the storage node Q & QB stores the previous value of the data on that Cell node.

453

But, there are some drawbacks in 10T SRAM Cell which reduces the stability of Cell during modes operation to avoid this affects in low power. Either we have to reduce the threshold or we have to leave low voltage working.

Hence, for resolving this issue we switch from CMOS technology to FinFET (Double Gate MOSFET) [17].

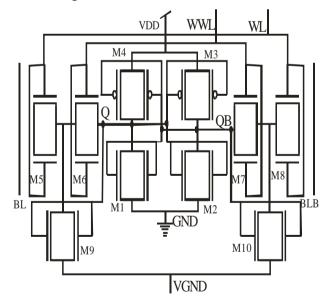

#### 3. PROPOSED FINFET BASED 10T SRAM CELL

The working of proposed FinFET based 10T SRAM Cell is same as CMOS based 10T SRAM Cell, into which we just changes the device from single gate to double gate MOSFET as shown in figure 3 FinFET based 10T SRAM Cell. As we know, weak writability is another issue for subthreshold SRAM Cell. In FinFET based 10T SRAM Cell contains series of access transistors in which writability is also a major concern [18]. VDD is getting distorted to enhance the writability due to different-different value which is nearer in low power value. VDD lines are share between the access transistors hence it degrades the hold stability of SRAM Cells. To avoid this issue, each row has to provide separate and individual VDD lines to operate successfully, resulting that cell size increases due to that poly pitch get affected in cell layout. To improve writability we enhance the voltage of WL and WWL by 0.1V in 0.3V VDD to reimburse the weak writability [19]. The schematic diagram of 10T SRAM Cell is shown in figure 3.

#### 4. TRANSISTOR WIDTH MODULATION EFFECTS

The SNM of Read and Write Margin of 10T SRAM cell are affected by the transistor width modulation. The proper sizing of Driver transistor is responsible for a drastic change in the value of SNM. The Cell Ratio and Pull up Ratio affects the stability of the SRAM Cell [20]. The approach that helps to calculate static noise margin is butterfly method. The SNM depends on the following: cell ratio (CR), supply voltage & pull up ratio (PR). 70% stability of SNM is depends on the driver transistors. But, before we can know SNM we have to know the definition of CR and PR. Cell Ratio (CR) is the ratio between sizes of the driver transistor to the load transistor during the read operation.

$$Cell \ Ratio = \frac{Size \ of \ pull \ down \ transistors}{Size \ of \ access \ transistors}$$

(1)

Pull up ratio between sizes of the load transistor to the access transistor during write operation. It also fully depends on the size of the transistor [21]. Due to higher speed of evaluation for PMOS transistors in subthreshold mode, read and write cycle speed are improved.

$$Pull up Ratio = \frac{Size of pull up transistors}{Size of access transistors}$$

(2)

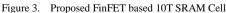

## 5. STATIC NOISE MARGIN

The basic SNM is obtained by mirroring the inverter characteristics and finding the maximum possible square between them. SNM affect both read and write margin that is related to the threshold voltages of the transistors in SRAM Cells [22]. The SNM at 0.7V of 10T SRAM Cell is shown in figure 4 Schematic diagram of 10T SRAM Cell on Static Noise Margin arrangement. The techniques are: 1) increasing the threshold voltage of the access transistors only (M5 & M8 and M6 & M7) changing the word-lines WL & WWL voltage level from VDD in different modes in which we are working at the time of calculation.

A relation of SNM related to transconductance that is:

$$SNM \propto \sqrt{1 - \frac{l_{\rm sd}}{g_{\rm pmos}}} - \frac{l_{\rm sa}}{g_{\rm nmos}}$$

(3)

Where the  $I_{sd}$  is the saturation drain current of the driver transistor,  $I_{sa}$  is the saturation drain current of the access transistor and g is the transconductance.

Figure 4. Static Noise Margin establishment in 10T SRAM Schematic during write mode

## A. Write Noise Margin and Read Noise Margin

The minimum bl or blb voltage to change the state of SRAM cell from one state to another or from any state to distorted state is write margin. The value of write margin is a function of cell design either symmetric in nature and process variation W/L ratio variation [23].

Write margin is directly proportional to the pull up ratio. In case when we are working on low power supply voltage then it will not help to complete the writing cycle. To discharge storage nodes in write cycle we have to use huge transistors for it. These problems in write margin can be hinder by taking some precautions. Out of this one method in write cycle is to insulate the M3 & M4 from supply voltage. But, this increases the area and reliability also affected.

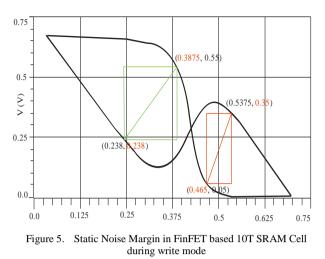

In 10T SRAM Cell WL and WWL both increases the control over write access but area also increases but it help to isolate the VDD. Based on the transistors current model we can calculate the read noise margin [24]. In calculation of SNM we get the function of the transistor's threshold voltage, power supply and also temperature variation we get the read margin. Read margin is directly proportional to cell ratio. In write mode the stability calculation shown below and its butterfly curve is shown in Figure 5 Static Noise Margin in FinFET based 10T SRAM Cell during write mode.

Calculation for Stability of FinFET based 10T SRAM cell at 100  $\ensuremath{\mathbb{C}}$

$$NM_{\rm H} = V_{\rm OH} - V_{\rm IH} \tag{4}$$

$$NM_{L} = V_{IL} - V_{OL}$$

(5)

$$SNM = \sqrt{(NM_{H}^{2}) + (NM_{L}^{2})}$$

(6)

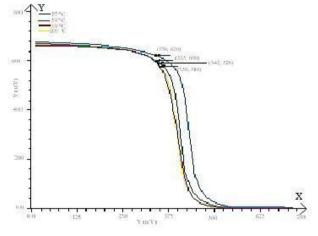

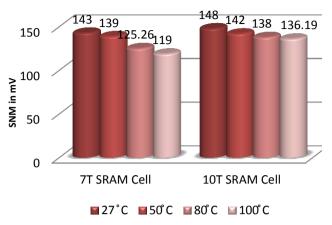

Variation of temperature affects the stability as shown in figure 6 Static Noise Margin of FinFET based 10T SRAM Cell with Temperature. As the temperature we vary the butterfly size varies, so the Static Noise Margin also varies. Here, we vary the temperature from  $27^{\circ}$ C to  $100^{\circ}$ C. The variation is shown in Table 1 and comparison of SNM of write mode value is shown in the figure 7 Comparison of FinFET Based 7T and 10T SRAM Cell on various temperature ranges.

TABLE I. Variation of SNM by varying Temperature

| FinFET<br>Based<br>SRAM<br>Cell | Temperature (in °C) |       |          |          |

|---------------------------------|---------------------|-------|----------|----------|

|                                 | 27                  | 50    | 80       | 100      |

| 7T SRAM<br>Cell                 | 143mV               | 139mV | 125.26mV | 119mV    |

| 10T<br>SRAM<br>Cell             | 148mV               | 142mV | 138mV    | 136.19mV |

Figure 6. Static Noise Margin of FinFET based 10T SRAM Cell with Temperature

Figure 7. Comparison of FinFET Based 7T and 10T SRAM Cell on various temperature ranges

#### 6. CONCLUSION

In IC designing the major concern we have to take is packaging (density) and lower leakage parameters in that denser medium, but still the reliability issues occurs in the circuitry. When discussing about memories in the IC then that time this issues we have to take seriously out of that Noise is the major issue which affects due to variation of temperature, low supply voltage, and variable threshold voltage. So, to find out the noise margin in SRAM Cell we are applying SNM butterfly curve calculation method on FinFET based 7T and 10T SRAM Cell. Out of that, FinFET based 10T SRAM Cell gives higher and perfect value compare to 7T SRAM Cell. In write mode, the value of SNM in FinFET based 7T SRAM Cell is 119mV but in FinFET based 10T SRAM Cell the SNM value is 148mV. FinFET based 10T SRAM gives improved results in Read SNM and also in Write SNM compare to 7T and 8T SRAM Cell because of its symmetric nature and also its more control over bit lines due to access transistors are double compare to all SRAM Cell. Also, we know that leakage parameters of any circuitry is getting doubled after every 10°C temperature but the variation in FinFET based 10T SRAM Cell is only varies from 138 to 148 mV but in 7T SRAM Cell its value is varies from 143 to 119mV which shows that the 7T SRAM Cell is less value of SNM value as compare to 10T SRAM Cell.

#### ACKNOWLEDGMENT

The author would like to thanks Malwa Institute of Science and Technology, Indore for supporting me to complete my research work and ITM University, Gwalior for providing the Cadence Tool with collaboration of Cadence System Design for the work to be completed.

#### REFERENCES

- Shin-ichi O'uchi, Kazuhiko Endo, Meishoku Masahara, Kunihiro Sakamoto, Yongxun Liu, Takashi Matsukawa, Toshihiro Sekigawa, Hanpei Koike and Eiichi Suzuki, "Flex-pass-gate SRAM for static noise margin enhancement using FinFET-based technology," Elsevier-Solid-State Electronics, vol. 52, pp. 1694-1702, Jul. 2008.

- [2] Mohammad Ansari, Hassan Afzali-Kusha, Behzad Ebrahimi, Zainalabedin Navabi, Ali Afzali-Kusha and Massoud Pedram, "A near-threshold 7T SRAM cell with high write and read margins and low write time for sub-20 nm FinFET technologies," Elsevier-Integration, The VLSI Journal, vol. 50, pp.91-106, Jan. 2015.

- [3] Hooman Farkhani, Ali Peiravi and Farshad Moradi, "A new asymmetric 6T SRAM cell with a write assist technique in 65 nm CMOS technology," Elsevier-Microelectronics Journal, vol. 45, pp. 1556-1565, Oct. 2014.

- [4] G. Hubert, L. Artola and D. Regis," Impact of scaling on the soft error sensitivity of bulk, FDSOI and FinFET technologies due to atmospheric radiation," Elsevier-Integration, The VLSI Journal, vol. 50, pp.39-47, Jan. 2015.

- [5] Takashi Matsukawa, Kazuhiko Endo, Yongxun Liu, Shinichi O'uchi, Yuki Ishikawa, Hiromi Yamauchi, Junichi Tsukada, Kenichi Ishii, Kunihiro Sakamoto, Eiichi Suzuki and Meishoku Masahara," Dual metal gate FinFET integration by Ta/Mo diffusion technology for Vt reduction and multi-Vt CMOS application," Elsevier-Solid-State Electronics, vol. 53, pp. 701-705, Apr. 2009.

- [6] Sherif A. Tawfik and Volkan Kursun," FinFET domino logic with independent gate keepers," Elsevier-Microelectronics Journal, vol. 40, pp. 1531-1540, Mar. 2009.

- [7] T. Cakici, K. Kim, and K. Roy, "FinFET based SRAM design for low standby power applications" IEEE 8<sup>th</sup> International symposium on Quality Electronic Design, pp. 127-132, Mar. 2007, San Jose, CA.

- [8] Achiranshu Garg and Tony Tae-Hyoung Kim, "SRAM Array Structures for Energy Efficiency Enhancement," IEEE Transactions on Circuits and Systems—II, vol.60, no.6, pp.351-355, June 2013.

- [9] J. Ouyang and Y. Xie "Power optimization for FinFET-based circuits using genetic algorithms" IEEE International System-on-Chip Conference, pp. 211-214, Sept. 2008, Newport Beach, CA.

- [10] Ajay N. Bhoj and Niraj K. Jha," Parasitics-Aware Design of Symmetric and Asymmetric Gate-Work function FinFET SRAMs," IEEE Transactions On Very Large Scale Integration Systems, pp. 1-14, 2013.

- [11] Sumeet Kumar Gupta, Jaydeep P. Kulkarni and Kaushik Roy, "Tri-Mode Independent Gate FinFET-Based SRAM with Pass-Gate Feedback: Technology–Circuit Co-Design for Enhanced Cell Stability," IEEE Transactions on Electron Devices, vol. 60, no. 11, Nov. 2013.

- [12] Debajit Bhattacharya and Niraj K. Jha, "TCAD-Assisted Capacitance Extraction of FinFET SRAM and Logic Arrays," IEEE Transactions on Very Large Scale Integration Systems, 2013.

- [13] Xue Lin, Yanzhi Wang, and Massoud Pedram "Joint Sizing and Adaptive Independent Gate Control for FinFET Circuits Operating in Multiple Voltage Regimes Using the Logical Effort Method," IEEE International Conference on Computer Aided Design, vol. 18, no.21, pp.444-449, Nov. 2013, San Jose, California.

455

[14] Shyam Akashe, Sushil Bhushan, Sanjay Sharma "High Density and Low Leakage Current Based 5T SRAM Cell Using 45nm Technology," Romanian Journal of Information Science and Technology, vol.15, no.2, pp. 155-168, Dec. 2012.

456

- [15] Ik Joon Chang, Jae-Joon Kim, Sang Phill Park and Kaushik Roy, "A 32 kb 10T Sub-Threshold SRAM Array With Bit-Interleaving and Differential Read Scheme in 90 nm CMOS," IEEE Journal of Solid-State Circuits, vol. 44, no. 2, pp. 650-658, Feb. 2009.

- [16] P. Upadhyay, R. Kar, D. Mandal and S.P. Ghoshal, "A design of low swing and multi threshold voltage based low power 12T SRAM cell," Elsevier- Computers and Electrical Engineering, Oct. 2014.

- [17] Liang Wen and ZhentaoLi and YongLi, "Single-ended, robust 8T SRAM cell for low-voltage operation," Elsevier- Microelectronics Journal, vol. 44, May 2013.

- [18] Hooman Farkhani, Ali Peiravi and Farsad Moradi, "A new write assist technique for SRAM design in 65nm CMOS technology," Elsevier-Integration, the VLSI Journal, vol. 50, pp. 16-27, Jun. 2015.

- [19] Bo Wang, Jun Zhou and Tony Tae-Hyoung Kim, "SRAM devices and circuits optimization towards energy efficiency in multi-Vth CMOS," Elsevier-Microelectronics Journal, vol.46, no.3, pp. 256-272, Mar. 2015.

- [20] Dae-Young Jeon, So Jeong Park, Mireille Mouis, Sylvain Barraud, Gyu-Tae Kim and Gérard Ghibaudo, "Effects of channel width variation on electrical characteristics of tri-gate Junctionless transistors," Elsevier-Solid-State Electronics, vol.81, pp. 58–62, 2013.

- [21] Varun sable, shyam akashe, "Enactment of FinFET Based SRAM with Low Power, Noise and Data Retention at 45nm Technology," proceeding of Springer, International Conference on Opto-Electronics and Applied Optics (IEM OPTRONIX), Institute of Engineering & Management, Kolkata, 17-18 Dec. 2014 (Springer).

- [22] Ting-Hsiang Huang, Hsin-Cheng Lai, Bo-Jie Tzeng and Zingway Pei, "Air stable organic complementary inverter with high and balance noise margin based on polymer/metal oxide hybrid gate dielectrics," Elsevier- Organic Electronics, vol. 13, pp. 1365– 1369, 2012.

- [23] Liviu Oniciuc, Petru Andrei, "Sensitivity of static noise margins to random dopant variations in 6-T SRAM cells," Elsevier-Solid-State Electronics, vol. 52, pp. 1542-1549, Jul. 2008.

- [24] Chika Tanaka , Masumi Saitoh, Kensuke Ota and Toshinori Numata, "Analysis of static noise margin improvement for low voltage SRAM composed of nano-scale MOSFETs with ideal subthreshold factor and small variability," Elsevier-Solid-State Electronics, vol. 109, pp. 58-62, Mar. 2015.

**Mr. Varun Sable** was born on 4<sup>th</sup> March 1990. The author received his M.Tech from ITM University, Gwalior, Madhya Pradesh, India in year 2015. The title of thesis is Recital Study of 1Kb Array of FinFET based 10T SRAM Cell. The author's major fields of study are low power VLSI Design and memory. He has published about 4 referred

journal and Conference papers. His important research publications are "Enactment of FinFET Based SRAM with Low Power, Noise and Data Retention at 45nm Technology," proceeding of Springer, International Conference on Opto-Electronics and Applied Optics 2014; "Noise Voltage Apportioned a New Reliability Concern in Low Power 10T SRAM Cell Using FinFET Device," American Scientific Publication, 2015. The author also have patent "Memory device with Non-Volatile Memory Array including One FinFET One Memristor (1F1M)," sept 2015.

**Dr. Shyam Akashe** was born in Achalpur (Maharashtra) India on 22<sup>nd</sup> May 1976. He did M.Tech in Electronics & Communication Engineering from Rajiv Gandhi Proudyogiki Vishwavidyalaya (RGPV), Bhopal in 2006 and Ph.D Thapar University, Patiala (previously Thapar Institute of Engineering

and Technology), Punjab in 2013. Dr. Akashe worked as Assistant Professor at Institute of Technology & Management (ITM) Gwalior. Currently, he is working as Professor and Postgraduation Coordinator, Electronics & Communication Engineering department at ITM University Gwalior. Dr. Akashe is authored/co-authored more than 200 research papers in peer reviewed international/national journals and conferences. He has also published 5 patent, 2 books and 1 chapter.His biography published in Marquis's Who's Who in Engineering Field, USA awarded by Marquis, 2015.

His areas of research are Low Power VLSI Design, Modeling, FinFET based memory design, Circuits for future VLSI Technology, Digital Design and FPGA implementation. He is life member of the Institution of Engineers (IE), Life Member of the Indian Society for Technical Education (IETE), Life Member of the Indian Society for Technical Education (ISTE) and Life Member of the Instrumentation Society of India (ISOI), also he is member of VLSI Society of India (VSI). Dr. Akashe is editorial board member of the IEEE African Journal of Computing & ICTS (IEEE Nigeria). He is also a reviewer for IEEE Transaction on VLSI Systems, IEEE Transactions on Nanotechnology, International Journal of Electronics (Taylor and Francis), Microelectronics Journal (Elsevier).