ISSN (2210-142X)

Int. J. Com. Dig. Sys. 9, No.5 (Sep-2020)

http://dx.doi.org/10.12785/ijcds/090516

# Low Power Implementation of FIR Filter for De-Noising the EOG Signal

### Gundugonti Kishore Kumar<sup>1</sup> and Balaji Narayanam<sup>2</sup>

<sup>1</sup> Department of Electronics and Communication Engineering, V R Siddhartha Engineering College, Vijayawada, India <sup>2</sup> Department of Electronics and Communication Engineering, JNTUK University College of Engineering, Kakinada, India

Received 24 Nov. 2019, Revised 13 May 2020, Accepted 25 Aug. 2020, Published 1 Sep. 2020

**Abstract:** In this paper, we propose a modified FIR filter using canonical signed digit representation and compressor techniques for de-noising the Electrooculography signal (EOG). A dipole, formed between cornea and retina in an eye, resulting in voltage difference with occurrence of eye movement, which in turn generates an electrical signal. These electrical signals, called Electrooculography (EOG) signal and are useful in many medical and bioelectrical applications. To remove the noise in EOG signal an enhanced 16-bit FIR filter is used. The proposed FIR architecture uses canonical signed digit based multipliers and 3:2 or 4:2 compressors to achieve greater improvement in power and delay compared to conventional shift-add method of multiplication. Canonic signed digit (CSD) is used in order to reduce the design complexity of the multiplication by representing the filter coefficients in CSD format. Instead of using Carry Look Ahead adders, 4:2 compressors are used. The proposed approach is implemented on FPGA development kit.

Keywords: Electro-oculography, Canonic Signed Digit, Compressors, FPGA

### 1. Introduction

Electrooculography (EOG) is one of the bio-signals that can be measured and monitored. It is a technique for measuring the cornea-retinal standing potential that exists between the front and the back of the human eye. The resulting signal is Electrooculogram. The EOG signal provides the corresponding voltage generated by the eye movement. These measurements are used to study the eye movement pattern and related aspects [1]. Amplitude of this signal ranges between 50-3500 µV and its frequency component ranges from 5-30Hz [2]. Main applications of EOG signals are in ophthalmological diagnosis, recording eye movement and in many Human Computer Interface. EOG has wide range of applications in medical diagnosis, study of different eve movements and Human Machine Interface (HMI). Many noise suppressions techniques for EOG signals have been implemented; out of them band pass FIR filter has accuracy and best processing speed [3]. Multipliers are important and building blocks in Digital Signal Processing, Digital Image Processing.[4] Hence to reduce the complexity in multiplication and to reduce path delays, area of the existing conventional methods, CSD based representation is very effective [5]. CSD representation will be useful for many designimplementation of digital filters and CSD based filter architecture for image conversion [6].

This paper describes the denoising of EOG signal using FIR filtering techniques. Section 2 describes the FIR filter basics. Section 3 focuses on conventional method of multiplication. Proposed method and its implementation in FPGA along with Software/Hardware co-simulation is discussed in sections 4 and 5. Synthesis Results of proposed architectures are mentioned in sections 6. Conclusion is discussed in last section.

### 2. FIR FILTER

Digital filter is one of the most important block in DSP processing. It has many applications like noise reduction and suppression of unwanted signals. As it resolves to zero in finite time, hence it has an impulse response of finite duration. The equation of FIR filter is as shown below,[7]

$$Y(n) = \sum_{k=0}^{N-1} h(k) * x(n-k)$$

(1)

Where x (n) is input sample, Y (n) is output sample, Y (k) is filter coefficient, and Y is filter order. Eq. (1) represents FIR filter of order Y. The term Y (n-k) in (1)

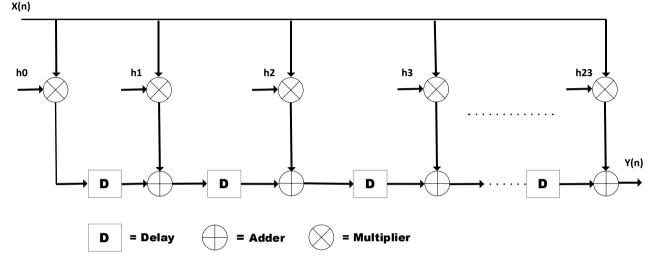

represents the input to multiplication process with some delay, which is called as taps. These define the filter order in different forms of FIR structures. Basic FIR filter with transposed form is shown in Fig.1. FIR filter Transpose form is having more advantages than direct form [8]. The major building blocks of FIR filter are multiplier, adders and delays. Here multipliers should be fast enough so that overall throughput should not suffer. Multiplication blocks uses adders in combination and delays are used to store

sample value in memory for one sample clock cycle. Filter coefficients are obtained by MATLAB FDA tool by designing the 16-bit low pass Equiripple FIR filter with frequency range of 5-30Hz. The obtained filter coefficients are [-192, -288, -352, 224, 864, 1696, 2624, 3552, 4256, 4640]. The designed filter is of 24-order, hence we get 24 filter coefficients in which 12 are mentioned above [h0-h11], remaining coefficients are symmetric in nature.

Figure 1. FIR Filter Architecture

### 3. CONVENTIONAL SHIFT-ADD MULTIPLIER

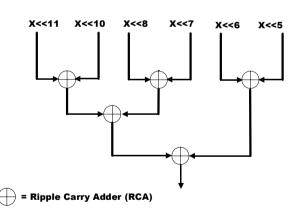

From the literature survey, it is found that in FIR filter, optimization can be done in multiplier block. Shift and add is a method for implementing binary multiplication. Here, the multiplication with the 0 bits is neglected hence number of commutations are reduced, hence number of logic devices will be reduced which in turn reduces their switching activities, which in turn impacts in reduction of the area and power [9]. Left shifting a binary number by n-bit is equivalent to multiplying the number by 2<sup>n</sup>. Shift-Add multiplication on each coefficient is performed by simply shifting the binary number by obtained shift values and adding all the results by using a Ripple Carry Adder (RCA). Filter coefficient 3552 (i.e., h9 and h14) has maximum path delay, hence representing the coefficient in binary form as: 0000 1101 1110 0000, which can be represented as follows: 211 +  $2^{10} + 2^8 + 2^7 + 2^6 + 2^5$ . Shift-and-Add multiplication has performed instead of a simple binary multiplication. Maximum number of RCAs required for this implementation is for the coefficient h9 and required adders are 5. Maximum delay is shown in Fig.2.

Figure 2. Shift-Add representation for maximum path delay coefficient in Filter

### 4. FIR FILTER WITH PROPOSED MULTIPLIER

To further optimize filter area and delay, in Shift and add technique the binary number, of filter coefficients represented in CSD form, as it is more efficient than binary representation. CSD is a representation in which number of non-zero terms becomes minimal. It uses ternary number system with digit set of (-1, 0, 1) instead of binary digit set (0, 1). The extra digit "-1", denoted as "1 bar" [10]. In CSD representation, two consecutive non-zero digits are not allowed, which means that 11 or -11 are invalid. There are minimum non-zero binary

elements in CSD representation, which results in reduced number of adders. Therefore, CSD representation implementation in hardware is more efficient, instead of binary representation [11]. Coefficients in CSD are represented as:

$$Y(n) = \sum_{r=0}^{B-1} X_r 2^r$$

(2)

Where Xr = 0, 1, -1 (represented as 1 bar)

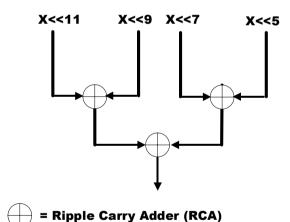

As Shift-Add, multiplication has 5 RCA, which takes long time for computation, hence to reduce number of RCA filter coefficients are represented in CSD format. For CSD representation, the critical path or the maximum delay for coefficient h7, maximum number of Ripple carry Adders (RCA) required for this is shown in Fig.3. From Fig.2, we get to know that minimum required number of RCAs for multiplication in FIR filter designed using shift-add method is 5 RCA. Where each RCA consists of 1 Half Adder (HA) and N-1 Full Adders (FA) [12]. Minimum required RCAs for CSD based representation is 3 RCA. The proposed multiplier uses less number of RCAs compared to conventional multiplier, and it consumes less area, power and delay than the conventional method.

Figure 3. CSD based Representationn for critical path delay coefficients in filter

Instead of using conventional RCA or CSA, ternary adders are proposed for designing an adder block [13]. Instead of using many stages of RCA, in first stage 3 inputs are compressed to two inputs using carry save adder, which are then processed using a normal RCA. The filter coefficients are then converted into CSD

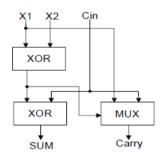

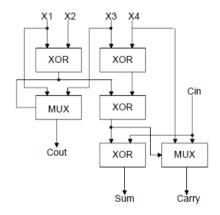

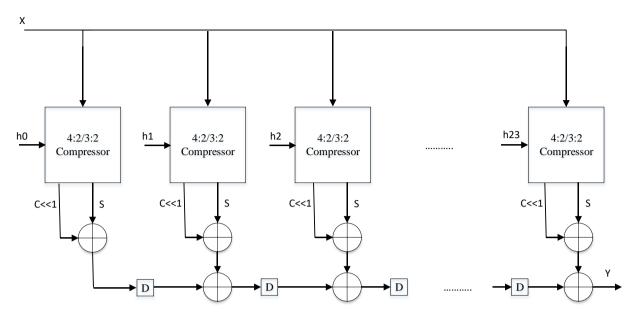

format, instead of normal binary representation. Instead of using conventional RCA, which uses more area and higher delay are replaced by a 3:2 or 4:2 compressors [14]. A 3:2 compressor takes 3 inputs and generates 2 outputs as Sum (S) and Carry (C) using XOR gates and MUX as shown in Fig.4. By using this implementation, we get an overall delay of two XOR gates and area is calculated as two XOR gates and one 2:1 MUX. Similarly 4:2 compressor implementation is comprised of two FA (Full Adders), where individual FA are divided into sub-blocks based on XOR gates as discussed in [15]. The optimized compressor design consists of four XOR gates and two 2:1 MUXs is shown in Fig.5. Hence we can observe the overall delay as three times the delay of XOR gates and area is calculated as two 2:1 MUXs and four XOR gates [16]. An RCA is required to add the final S (sum) and C (carry) outputs. FIR Filter with the proposed multiplier architecture is shown in Fig.6

Figure 4. 3:2 Compressor using XOR and MUX gates

Figure 5. 4:2 Compressor using XOR gates

Figure 6. FIR filter using the proposed multiplication architecture

Figure 7. Hardware/Software Co-Simulation Setup For Noise Removal In EOG Signal

Figure 8. Waveforms of Raw EOG signal and Denoised EOG signal

### 5. IMPLEMENTATION OF FILTER WITH PROPOSED ARCHITECTURE

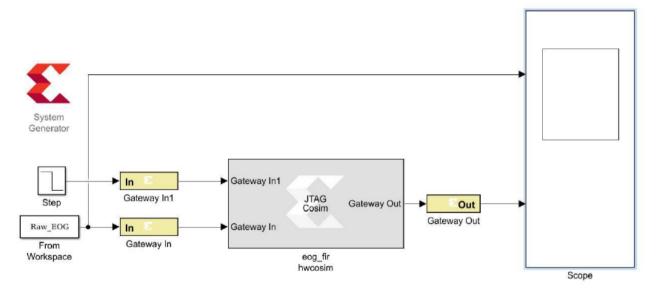

The setup for removing noise in EOG signal using proposed method is implemented using Verilog HDL and MATLAB, and hardware/software co-simulation is used. Initially simulation results are verified and then functionality is implemented in hardware/software co-simulation block. In this proposed architecture EOG signal is obtained from [17]. The proposed model is implemented and verified on FPGA Zed Board Zynq evaluation and development kit xc7z020c1g4841 using Xilinx System Generator (XSG) 2016.2. The hardware/software co-simulation setup is shown in Fig.7.

The applied raw EOG signal and its filtered output signal is observed on the scope in XSG. The JTAG cosimulation in XSG generates the Xilinx block set required for the hardware zed board. The output waveform of raw EOG and noise removed EOG signal is shown in Fig.8. The Power Delay Product (PDP) of CSD is increased by 6.73% than the shift-add method and the Power Delay Product of proposed compressor based architecture is increased by 10.24% than the conventional shift-add method.

### 6. SYNTHESIS RESULTS

In this section, synthesis results of proposed and conventional filter is shown, by comparing their area, power and delays. The results are obtained from cadence 90nm technology design tool. Implementation results of conventional and proposed multipliers is shown in Table 1. Which displays parameters like Delay, Area and Power along with Area Delay Product (ADP), Power Delay Product (PDP), increase in ADP (ADP%), PDP (PDP%), and increase in delay (D%) is also listed in Table 1.

TABLE 1. SYNTHESIS RESULTS OF FIR WITH DIFFERENT MULTIPLICATION TECHNIQUES

| Parameter       | Shift_Add | CSD       | Proposed |

|-----------------|-----------|-----------|----------|

| $Area(\mu m^2)$ | 30795     | 30009     | 30491    |

| $Power(\mu W)$  | 5212.67   | 5031.60   | 5116.81  |

| Delay(nS)       | 7.94      | 7.19      | 6.51     |

| D(-)%           |           | 9.45      | 22.08    |

| PDP             | 41409.47  | 36192.31  | 33295.05 |

| <i>PDP</i> (-)% |           | 12.60     | 19.60    |

| ADP             | 244635.5  | 215854.74 | 198404.9 |

| ADP(-)%         |           | 11.76     | 18.90    |

The proposed architecture has reduced delay compared to conventional methods as shown in Table 1, because of using ternary adders instead of conventional adders. EOG signal can be used to analyze various eye movements such as saccades, fixational movements and vergence. Many eye diseases such as degenerative myopia, retinal disorders, and epileptic nystagmus can be diagnosed. EOG has Drowsiness detection, HMI, and eye-tracking for bio-medical engineering applications.

### 7. CONCLUSION

In this, we have proposed a modified FIR filter for denoising the EOG signal. In this proposed filter architecture, it uses CSD based representation for minimizing the multiplication and a conventional adders is replaced by 3:2/4:2 compressors. The proposed architecture is compared with the conventional method of shift-add and CSD with RCA and improvements is shown in terms of area, power and delay. The filters have been synthesized and implemented in Zynq development kit

using Vivado Design suit to target the device xc7z020c1g4841. Results show that improvement in PDP, ADP for this filter.

### REFERENCES

- [1] Daud, W. M. B. W., & Sudirman, R. (2011). Time Frequency Analysis of Electrooculograph (EOG) Signal of Eye Movement Potentials Based on Wavelet Energy Distribution. 2011 Fifth Asia Modelling Symposium. doi:10.1109/ams.2011.26.

- [2] Merino, M., Rivera, O., Gomez, I., Molina, A., & Dorronzoro, E. (2010). A Method of EOG Signal Processing to Detect the Direction of Eye Movements. doi:10.1109/sensordevices.2010.25.

- [3] Dasgupta, A., Chakrborty, S., Chaudhuri, A., & Routray, A. (2016). Evaluation of denoising techniques for EOG signals based on SNR estimation. 2016 International Conference on Systems in Medicine and Biology (ICSMB). doi:10.1109/icsmb.2016.7915110.

- [4] M.Lakshmi Kiran, K.V. Ramanaiah, "Design and Implementation of High Speed Radix-2 CSD Based Floating Point Multiplier", International Journal of Scientific Research in Multidisciplinary Studies, Vol.3, Issue.7, pp.17-22, 2017.

- [5] Ruiz, G. A., & Granda, M. (2011). Efficient canonic signed digit recoding. Microelectronics Journal, 42(9), 1090– 1097. doi:10.1016/j.mejo.2011.06.006.

- [6] Lee, H., & Sobelman, G. E. (2002). FPGA-based digit-serial CSD FIR filter for image signal format conversion. Microelectronics Journal, 33(5-6), 501–508. doi:10.1016/s0026-2692(01)00137-9.

- [7] Trimale, M. B., & Chilveri. (2017). A review: FIR filter implementation. 2017 2nd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT). doi:10.1109/rteict.2017.8256573.

- [8] Parvin, K. N., & Hussain, M. Z. (2018). Multiplication techniques for an efficient FIR filter design for hearing aid applications. 2018 2nd International Conference on Inventive Systems and Control (ICISC). doi:10.1109/icisc.2018.8398944.

- [9] Singh, T. H., Pritamdas, K., & Laishram, R. (2017). Low power VLSI transposed structure FIR filter using shift/add architecture. 2017 2nd International Conference for Convergence in Technology (I2CT). doi:10.1109/i2ct.2017.8226290

- [10] Hartley, R. I. (1996). Subexpression sharing in filters using canonic signed digit multipliers. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 43(10), 677–688. doi:10.1109/82.539000

- [11] Sharma, A., & Rawat, T. K. (2019). Design and FPGA implementation of lattice wave fractional order digital differentiator. Microelectronics Journal. doi:10.1016/j.mejo.2019.04.013.

- [12] Paldurai, K., Hariharan, K., Karthikeyan, G. C., & Lakshmanan, K. (2014). Implementation of MAC using area efficient and reduced delay vedic multiplier targeted at FPGA architectures. 2014 International Conference on Communication and Network Technologies. doi:10.1109/cnt.2014.7062762.

- [13] Kumm, Martin & Zipf, P.. (2014). Efficient high speed compression trees on Xilinx FPGAs. Methode. und Beschreib. Zur. Modellier. und Verif. Von. Schalt. und Syst.. 171-182.

- [14] Mandal, A., Mishra, R., Kaushik, B. K., & Rizvi, N. Z. (2015). Design of LMS Adaptive Radar Detector for Non-homogeneous Interferences. IETE Technical Review, 33(3), 269–279. doi:10.1080/02564602.2015.1093436

- [15] C. Chang, J. Gu, M. Zhang, "Ultra Low-Voltage Low- Power CMOS 4- 2 and 5-2 Compressors for Fast Arithmetic Circuits," IEEE Transactions on Circuits & Systems, Vol. 51, No. 10, pp. 1985-1997, Oct. 2004.

- [16] Veeramachaneni, S., Krishna, K., Avinash, L., Puppala, S., & Srinivas, M. B. (2007). Novel Architectures for High-Speed and Low-Power 3-2, 4-2 and 5-2 Compressors. 20th International Conference on VLSI Design Held Jointly with 6th International Conference on Embedded Systems (VLSID'07). doi:10.1109/vlsid.2007.116

- [17] A. Bulling, J. A. Ward, H. Gellersen and G. Troster, "Eye Movement Analysis for Activity Recognition Using Electrooculography," in IEEE Transactions on Pattern Analysis and Machine Intelligence, vol. 33, no. 4, pp. 741-753, April 2011.

Kishore Kumar Gundugonti is working as Assistant Professor in the Department of ECE at Velagapudi Ramakrishna Siddhartha Engineering College, Vijayawada, Andhra Pradesh, India. He received his B.TECH. degree from department of ECE at JNTU, Hyderabad in 2005.

M.TECH. degree from department of ECE at JNTU, Hyderabad in 2008. He is pursuing his Ph.D.

degree in JNTU, Kakinada, Andhra Pradesh, India. His current research interests include Biomedical signal processing and VLSI System Design.

Balaji Narayanam is working as Director Admissions, Professor of Electronics and Communication Engineering Jawaharlal Nehru Technological University Kakinada. He has more than 22 years of experience in teaching and research. He received his B.E Electronics & Communication Engineering from Andhra University in the year 1996. M.E.

Digital Systems from Osmania University in the year 2002. He has more than 22 years of experience in teaching and research. He published more than 50 Research papers in National, International Journals, and Conferences. He is an expert in VLSI and Signal Processing.

## **International Journal of Computing and Digital Systems** ISSN (2210-142X)

Int. J. Com. Dig. Sys. 9, No.5 (Sep-2020)