### **FPGA-Based MWD for Network Error Correction**

Wael M. El-Medany

Computer Engineering Department, College of Information Technology, University Of Bahrain, 32038 Bahrain,

Received: 15 Jan. 2015, Revised: 16 April 2015, Accepted: 20 April 2015, Published: (1 May) 2015

Abstract: This paper presents reconfigurable hardware architecture for MWD (Minimum Weight Decoding) algorithm for network error correction, with high throughput on Field Programmable Gate Array (FPGA). Network Error Correction (NEC) is used for detecting and correcting the errors in noisy communication channels when multicasting a source message to a set of nodes. Minimum Weight Decoding (MWD) algorithm is a cyclic linear block codes that are used as Forward Error Correcting (FEC) codes. The design can be reconfigured for different message length and different generator number, the encoder and decoder has been described using VHDL (VHSIC Hardware Description Language). The decoder has the ability to detect and correct different types and different numbers of errors based on the message length and the length of redundant data. The design has been simulated and tested using ModelSim PE student edition 10.4. Spartan 3 FPGA starter kit from Xilinx has been used for implementing and testing the design in a hardware level.

Keywords: FPGA; MWD; VHDL; Embedded Networks

#### **1. INTRODUCTION**

Error Correcting Code (ECC) is a technique used to increase link reliability and to lower the required transmitted power. A detailed description of Error Correcting Code have been given by Egner, 2011; Etzion and Vardy, 2011; Frigo and Stewart, 2014; Huffman and Pless, 2003; Islam, 2010; Morelos-Zaragoza, 2006; Naseer and Draper, 2008a, ECC enables reconstruction of the original data at the receiving end of the communication channel [1-7]. In (Chang et al., 2010) the main role of Forward Error Correction (FEC) is given, it plays the main role for correcting errors in computer networks, particularly when poor Signal to Noise Ratio (SNR) environments are encountered [8]. In FEC the encoder adds redundant information that allows the receiver to detect and possibly estimate the error location, and hence correct the detected error, for that reason FEC is a suitable ECC technique when single source is broadcasting data to many destinations, as it does not require handshaking between sender and receiver.

The concept of Network Error Correction (NEC) codes has been introduced by Cai and Yeung, 2002, 2006; Zhang, 2008, 2011, as a generalization of classical error correction codes, especially when a

source message is transmitted to a set of receiving nodes on a network [9-12].

Minimum weight decoding algorithm is a cyclic linear block coding technique that has the ability of detecting and correcting channel errors in an efficient and reliable manner, the hardware of MWD algorithm has been described by El-Medany et al., 1998; El-Medany et al., 2001, the algorithm has been discussed by Martin et al., 1995; Naseer and Draper, 2008a, b; Peters, 2010; Vardy, 1997, it is a modified version of a well-known error trapping technique that use cyclic shifting for trapping the error [3, 13-18].

In this paper we are introducing the idea of using the well-known MWD decoding technique with reconfigurable architecture in error detection and correction for noisy communication channels in computer networks. The materials in this paper are organized as follows: after this introduction section, a brief discussion about error correcting codes is given in section 2; in section 3, a parity-check encoding and decoding techniques are summarized; the syndrome linear block decoding technique is discussed in section 4; in section 5 we are discussing the VHDL design flow for both ASIC and FPGA designs; reconfigurable architecture is given in section 6; section 7 discuss the

E-mail address: welmedany@uob.edu.bh

hardware implementation and RTL design; simulation results are discussed in section 8; and finally the conclusion is given in section 9. *Wael Elmedany: FPGA-Based MWD* ...

#### 2. ERROR-CORRECTING CODES

Error-correcting codes are types of error control coding techniques that are used a noisy communication channel to detect and correct errors at the receiving end in case of forward error correction, they have been described by Bruen and Forcinito, 2011; Huffman and Pless, 2003; Peterson and Weldon, 1972, [7, 19, 20]. The channel may be a high frequency radio link, a Public Telephone Network (PTN), or a Global System for Mobile communication (GSM) network [21, 22].

For example, if a stream of binary data (zeros and ones) is going to be sent through a noisy channel as quickly and as reliably as possible. The error could be due to thermal noise, faults in electronic equipment, human errors, or lightning, etc.

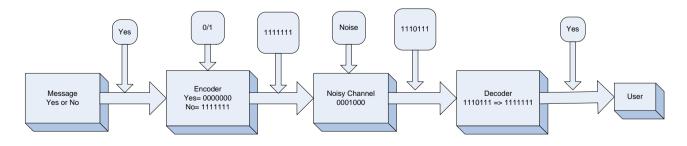

Fig. 1 shows an example of a simple error-correcting code, in the form of a binary repetition code. Here the encoder is repeating the message symbol seven times. The other r = 6 bits are repetitions of the message digit. If there is one error that has occurred, the decoder will decode the received vector 1110111 as the "nearest" codeword that is 1111111 or No which is still correct.

## 3. PARITY-CHECK ENCODING AND DECODING

For free error transmission in a digital communication channel, the transmitted binary one will be received as a one, and transmitted zero will be received as a zero. When an error occurs, in a noisy channel, transmitted zero will be received as a one, and transmitted one will be received as zero. Such errors cannot be prevented; but can be reduced by coding techniques. Assume that a message of particular sequence of k-bits is going to be transmitted over a noisy channel; the transmitter must add some redundant bits or information based on some rules to help the receiver for detecting and possibly correcting the introduced error, this redundant information is the r check digits, it provide the receiver with sufficient information to enable it to detect and correct the channel errors, the length of the transmitted block will be (n = k + r). This issue is called the encoding problem; the message and the added information is called the codeword, it is any particular sequence of n digits that the encoder might transmit. There are  $2^k$  codewords available to be transmitted; this set of  $2^k$  codewords of length n is called the code [23, 24].

#### 4. SYNDROME DECODING

Syndrome decoding is an efficient linear block code that allows decoding of the received codeword over a noisy channel; it is a minimum distance decoding. Assume that a code  $\mathbf{C} \subset \mathbf{F}_2^n$  is a linear block code with (n) code length and minimum distance (dmin), the number of detected errors is given by:

$$\mathbf{X} = \lfloor \mathbf{d}_{\min} - \mathbf{1} \rfloor$$

Where **X** is the number of errors that can be detected, the capability of correcting errors is clearly given by:

$$\mathsf{t} = \left\lfloor \frac{\mathsf{d}_{\min} - 1}{2} \right\rfloor$$

Where **t** is number of errors that can be corrected. The implemented coding architecture is based on syndrom decoding that can trap the error, and then correct the error in the fly based on the redundant information provided by the parity-check equations [25, 26].

Figure 1. Block Diagram for Error Correcting Codes

Int. J. Com. Net. Teach. 3, No. 2, 59-68 (May 2015)

### 5. FPGA/ASIC DESIGN PROCESS USING VHDL

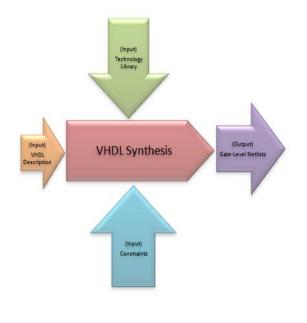

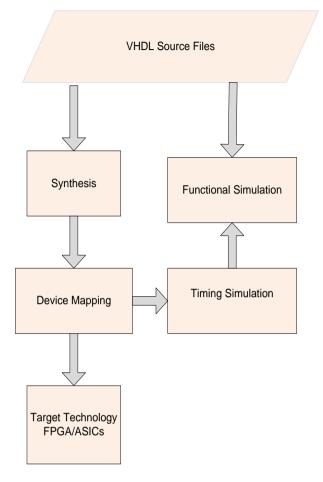

Application Specific Integrated Circuit (ASIC) and Field Programmable Gate Array (FPGA) are both customized chips that are used for particular applications; there are some advantages and disadvantages for each one of them, but in general FPGA becomes more attractive for its cost effective compared to ASIC especially for low volume of production. VHDL is a powerful hardware description language that allows complex design concepts to be expressed in a form similar to a computer program. It also allows the complex electronic circuits to be described in behavioral or structural modeling for circuit synthesis purposes or simulation purposes. Fig. 2 shows an overview of the VHDL synthesis process. VHDL source code can be used as the input to a simulator, allowing it to be functionally verified, or it can be passed to synthesis tools for implementation in a specified type of device. Fig. 3 shows simplified diagram for the VHDL design flow of the ASIC/FPGA design process. The flow diagram in Fig. 3 is a simplified one, some other diagrams it show the different levels of implementation for each one of the two target technologies (ASIC/FPGA) [27, 28]. The main differences between them is that FPGA does not require to reach the transistor level, in FPGA the implementation ends by generating a binary file (bit file) that will be used for FPGA configuration.

Figure 2. VHDL Synthesis Process

#### 6. RECONFIGURABLE ARCHITECTURE

Reconfigurable architecture is the ability of rapidly changing to achieve different functionalities of their components and the interconnection between them to a customized design. There most commercially available reconfigurable platform is the Field Programmable Gate Arrays (FPGAs). The main difference with the hardwired ASICs (Application Specific Integrated Circuits) is the possibility of loading a modified circuit of the design on the reconfigurable chip; on the other hand reconfigurable architecture has an advantage of rapid prototyping compared to ASICs that takes more time for long fabrication processing steps. The advantage of FPGA implementation compared to ASIC for the packet FEC architecture is that the design has a reconfigurable minimum distance according to the code length and generator polynomial with different message length as well.

# 7. HARWARE IMPLEMENTATION AND REGISTER TRANSFER LOGIC DESIGN

The MWD74 design has been synthesized and implemented on Xilinx FPGA chip. FPGAs solve the design challenges in most high-volume, cost-sensitive, I/O-intensive electronic applications. The Spartan-3AN FPGA family was the first Xilinx FPGA family that are RAM based with nonvolatile technology across a broad with different ranges of densities. The family the same features of the Spartan-3A FPGA family in addition to that it has a leading technology in-system flash memory for configuration and nonvolatile data storage.

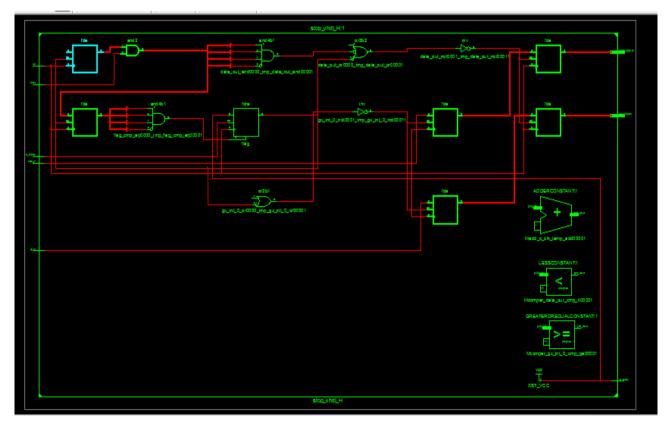

The synthesis process produces the Register Transfer Level (RTL), which is graphical representation of the HDL design module. The RTL produced by Xilinx Synthesis Technology (XST)) is generated by the synthesis tool. The goal of the RTL schematic view is to be as close as possible to the original VHDL code program. In the RTL schematic view, the design is represented in terms of basic building blocks, such as registers, multipliers, and adders.

Register Transfer Logic is a high level representation of the digital circuit that is normally generated from a synthesizable VHDL code program. The RTL abstraction generates a set of control signals that initiate the sequence of micro-operations in order to perform specific function. Register transfer logic is a design abstraction that models the sequential circuits in terms of the flow of control signals between the generated memory registers. In general the sequential circuits consist of memory element (registers) and combinational circuit. The combinational circuit consists of logic gates that can perform the logical functions in the digital circuit.

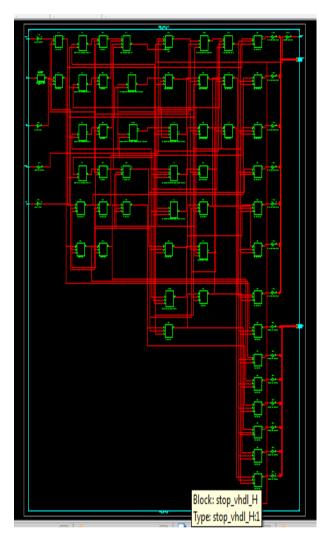

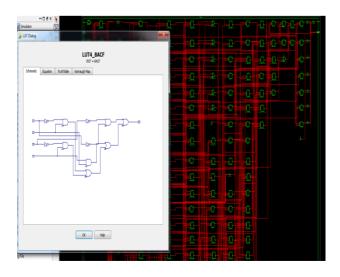

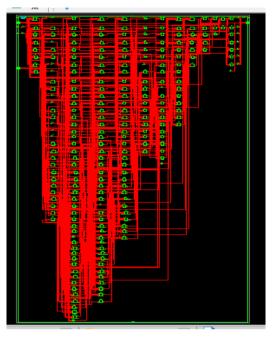

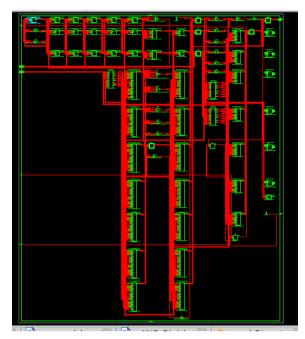

The registers synchronize the circuit's operation to the edges of the clock signal, and it is normally implemented as D flip-flops, and this is the memory part of the sequential circuit. In the latest version of Xilinx tools, there is another type of logic level representation, the technology schematic, which is normally based on using different types of Xilinx building block, most of them are Luck-Up Table (LUT). Fig. 4 shows the technology schematic for MWD74 Unit. Fig. 5 shows LUT4\_8ACF, which is one of the main building blocks that are shown in Fig. 4. In Fig. 6 the technology schematic for STOP Unit is shown. Fig. 7 and 8 show the RTL Schematic for MWD74 and STOP Units respectively. An example of RTL\_mux\_7 is given in Fig. 9.

Figure 4. Technology Schematic for MWD74 Unit

Figure 5. Xilinx LUT4\_8ACF

Figure 6. Technology Schematic for STOP Unit

Figure 7. RTL Schematic for MWD74 Unit

Figure 8. RTL Schematic for STOP Unit

63

| le Edit Tools Window Layout View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | es/bin/test/planAhead_run_i<br>Help                                |                 |                                          |             |                          |                            | Q - Search comma    | nds   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|------------------------------------------|-------------|--------------------------|----------------------------|---------------------|-------|

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    | - 🗶 🔌 🔪         | (2)                                      |             |                          |                            |                     |       |

| aborated Design -4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                                  |                 | ~                                        |             |                          |                            |                     |       |

| nysical Constraints 💷 🗆 🖄 🗡                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RTL Netlist                                                        | _ D & ×         | Device x                                 | RTL Schemat | ic 🗙 🧺 RTL Schematic (2) | × 🕍 RTL Schematic (3) ×    | RTL Schematic (4) × | 00    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I 1 1                                                              |                 | → <u>1 Instance</u>                      |             |                          |                            |                     |       |

| elab_constrs_1<br>-@ ROOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Stop_vhdl_H           ⊕-@ Nets (103)           ⊕-@ Primitives (26) |                 | + + <                                    |             | da                       | ata_int[6]_da              | ta_int[5]_mux_5     |       |

| et Properties _ □ L <sup>2</sup> ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |                 |                                          | .14.        |                          | d0[6: <u>0]</u><br>d1[6:0] | <u>o[</u> 6:0]      |       |

| Name: data_in Parent name: data_in Type: Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |                 |                                          | uala        | _in [>                   | conc                       | TRTL_mux_7          |       |

| General     Attributes     Instance Pins     Ali: 4     •       Image: Second state     Image: Second state     Image: Second state       Image: Second state     Image: Second state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |                 |                                          |             |                          |                            |                     |       |

| 'O Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |                 |                                          |             |                          |                            |                     | - 0 0 |

| Id Name Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Interface Neg Diff Pair                                            | Site Fixed Bank | I/O Std                                  | Vcco Vref   | Drive Strength Slew Typ  | e Pull Type                |                     |       |

| □ 1 dk Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |                 | default (LVCMOS25)                       |             |                          | NONE                       |                     |       |

| 2 d_enable Input     3 d_ready Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |                 | default (LVCMOS25)                       | 2 500       | 12 SLOW                  | NONE                       |                     |       |

| 3 d_ready Output<br>D 4 data_in Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |                 | default (LVCMOS25)<br>default (LVCMOS25) | 2.500       | 12 SLOW                  | NONE                       |                     |       |

| S data_out[0] Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |                 | default (LVCMOS25)                       | 2.500       | 12 SLOW                  | NONE                       |                     |       |

| G data_out[1] Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |                 | default (LVCMOS25)                       |             | 12 SLOW                  | NONE                       |                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |                 | default (LVCMOS25)                       |             | 12 SLOW                  | NONE                       |                     |       |

| 7 data_out[2] Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |                 | default (LVCMOS25)                       |             | 12 SLOW                  | NONE                       |                     |       |

| 7 data_out[2] Output<br>8 data_out[3] Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |                 | default (LVCMOS25)                       | 2.500       | 12 SLOW                  | NONE                       |                     |       |

| 7 data_out[2] Output           8 data_out[3] Output           9 data_out[4] Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |                 |                                          | 2.500       | 12 SLOW                  | NONE                       |                     |       |

| Image: Second |                                                                    |                 | default (LVCMOS25)                       |             |                          |                            |                     |       |

| 7 data_out[2] Output           8 data_out[3] Output           9 data_out[4] Output           10 data_out[5] Output           11 data_out[6] Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |                 | default (LVCMOS25)                       |             | 12 SLOW                  | NONE                       |                     |       |

| 7 data_out[2] Output           8 data_out[3] Output           9 data_out[4] Output           10 data_out[5] Output           11 data_out[5] Output           12 gx_in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |                 |                                          |             | 12 SLOW                  | NONE                       |                     |       |

| Image: Second |                                                                    |                 | default (LVCMOS25)                       |             | 12 SLOW                  |                            |                     |       |

| 7 data_out[2] Output           8 data_out[3] Output           9 data_out[4] Output           10 data_out[5] Output           11 data_out[5] Output           12 gx_in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |                 | default (LVCMOS25)                       |             | 12 SLOW                  |                            |                     |       |

Figure 9. Example of RTL\_mux\_7

## 8. SIMULATION RESULTS AND POWER CONSUMPTION

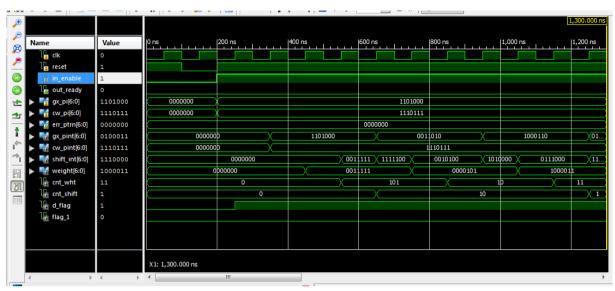

The design has been tested in simulation level and hardware level, the Simulation Results for MWD74 Unit is given in Fig. 10, the waveform in Fig. 10 has been generated using ISim simulator of Xilinx ISE 14.7, it has been tested also using ModelSim PE student edition 10.4. The design has an active low asynchronous reset, and active high input enable. The generator number is 4-bit within the 7-bit gx\_p signal; with the 3 MSBs are zeros. The signal cw\_p represents the received word that may contain an error.

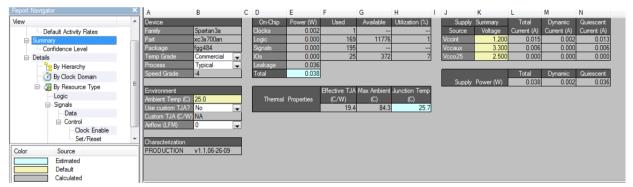

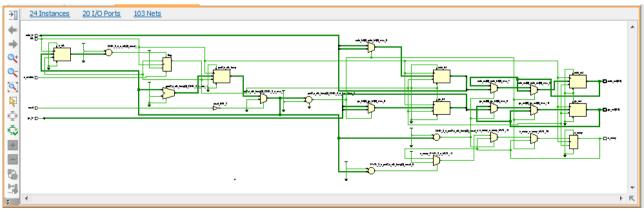

Fig. 11 shows a summary of power consumption, there are three different values that are given in Fig 11, the estimated value, the default value, and the calculated value. Fig. 12 shows the PlanAhead Synthesis for MWD Module, the PlanAhead process operates on the top module of the design after the design is synthesized, the design has 24 instances, 20 IO ports, and 103 nets. In Fig. 13, the summary of software version and target device, user Environment, and device usage statistics are given.

The used Operating System (OS) is NT64, the target family is Spartan 3A and Spartan 3AN, the target device is xc3s700an, the target package is fgg484, and the target speed is -4. Fig. 14 shows the summary of I/O Ports for MWD74 Module, it shows the list of inputs and outputs ports for the MWD74 Module, as well as the data width for each signal.

The Design Summary for MWD74 is given in Fig. 15, which shows the consumed resources from the target device (Spartan 3AN FPGA - xc3s 700an-4fgg-484). The summary shows the consumed number of 4-inputs LUTs, number of slices, number of slice flip flops, etc. The consumed resources reflects the cost of the circuit design, large number of consumed resources means high cost, and small number of consumed resources means low cost.

Figure 10. Simulation Results for MWD74 Unit

Figure 11. Summary of Power Consumption

Figure 12. PlanAhead Synthesis for MWD Modul

|                                    | nd Target D                          | evice                                                                            |                                                                                                                                                |                                                                        |                 |                                                              |                                                                                     |  |

|------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| Product Version:                   |                                      | ISE: 13. 1 (WebPack) - 0.4                                                       | 0d                                                                                                                                             |                                                                        | Target Family:  |                                                              | Spartan3A and Spartan3AN                                                            |  |

| 05 Platform:                       |                                      | NT64                                                                             |                                                                                                                                                |                                                                        | Target Device:  |                                                              | xc3s700an                                                                           |  |

| Project ID (randon                 | number)                              | 85b72e209d194541bdd7c                                                            | 60fed42eab3.871CF0F139F043                                                                                                                     | 710AAE4A7BAD1B4D84A.1                                                  | Target Package: |                                                              | fgg484                                                                              |  |

| Registration ID                    |                                      | 206763286_0_0_631                                                                |                                                                                                                                                | Target !                                                               |                 | -4                                                           |                                                                                     |  |

| Date Generated 2013-07-01T20:21:08 |                                      |                                                                                  |                                                                                                                                                |                                                                        | Tool Flow       |                                                              | ISE                                                                                 |  |

|                                    |                                      |                                                                                  |                                                                                                                                                |                                                                        |                 |                                                              |                                                                                     |  |

| User Environment                   |                                      |                                                                                  |                                                                                                                                                |                                                                        |                 |                                                              |                                                                                     |  |

| 05 Name                            | Micr                                 | osoft Windows 7 , 64-bit                                                         |                                                                                                                                                | 05 Release                                                             | Serv            | /ice Pack 1 (                                                | (build 7601)                                                                        |  |

| CPU Name                           | Inte                                 | (R) Core(TM) i3 CPU M 38                                                         | 0 @ 2.53GHz                                                                                                                                    | CPU Speed                                                              | 252             |                                                              |                                                                                     |  |

| Macro Statistics                   |                                      | neous Statistics                                                                 | Net Statistics                                                                                                                                 |                                                                        |                 | Site Usage                                                   |                                                                                     |  |

| Device Usage Stati                 | stics                                |                                                                                  |                                                                                                                                                |                                                                        |                 |                                                              |                                                                                     |  |

| ridero Statistics                  |                                      | ousStatistics                                                                    | NetStatistics                                                                                                                                  |                                                                        |                 | SiteSummar                                                   |                                                                                     |  |

|                                    | Plisceliane                          | ousotausues                                                                      | Netatausucs                                                                                                                                    |                                                                        |                 | SiteSummar                                                   | y .                                                                                 |  |

|                                    |                                      |                                                                                  |                                                                                                                                                |                                                                        |                 |                                                              |                                                                                     |  |

|                                    | • A(                                 | GG_BONDED_IO=3                                                                   | •NumNets_Active=6                                                                                                                              |                                                                        |                 | • IBU                                                        | F=2                                                                                 |  |

|                                    | • A(                                 | GG_IO=3                                                                          | <ul> <li>NumNodesOfType_A</li> </ul>                                                                                                           |                                                                        |                 | • IBU                                                        | F_DELAY_ADJ_BBOX=2                                                                  |  |

|                                    | • A(                                 | GG_IO=3<br>GG_SLICE=1                                                            | NumNodesOfType_A     NumNodesOfType_A                                                                                                          | ctive_DUMMYESC=2                                                       |                 | • IBU<br>• IBU                                               | F_DELAY_ADJ_BBOX=2<br>F_INBUF=2                                                     |  |